## 1 Description

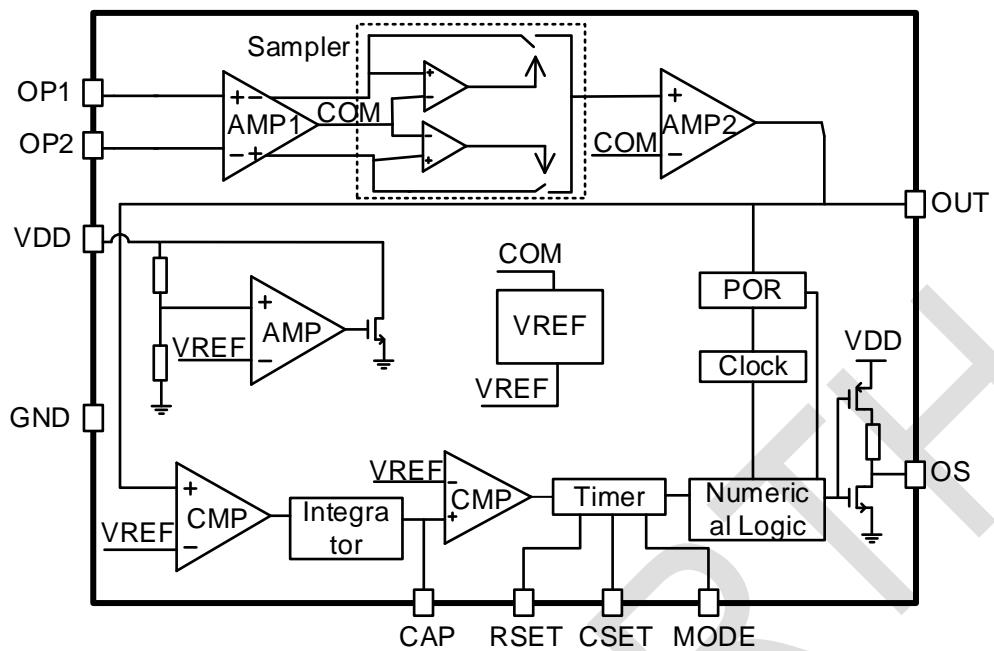

The CN54124 is a precision, low-power, Ground Fault Circuit Interrupter (GFCI) controller used for detecting ground fault leakage paths in electrical circuits, which can detect type A and type AC leakage currents. When the leakage current occurs on the L and N lines, the ZCT(zero current transformer) will detect the leakage current signal, the post-circuit converts the leakage current signal into a voltage signal and transmits it to the input terminal of the chip, when the peak value of the input voltage signal exceeds 4.95mV, the output pin of the chip generates a high level with a minimum duration of 20ms to drive the external SCR.

The CN54124 integrates functional modules such as regulated power supply, amplification circuit, comparison circuit, trip controller and trip drive circuit, and only needs current transformer and a small number of resistor capacitors externally.

## 2 Features

- Applied intype A and AC leakage detection

- High input sensitivity (4.95mV typical)

- Low quiescent current of 190uA

- Wide operating voltage range (3V~5.5V)

- Wide AC input voltage range:

50V~380V(50/60Hz)

- >20ms output pulse width can drive SCR

- Consistent leakage detection threshold

- Delay time can be adjusted

- Excellent EMC protection

- Wide operating temperature range (Ta=-40~+105°C)

## 3 Applications

- Ground Fault Circuit breakers

- Ground Fault Circuit relays

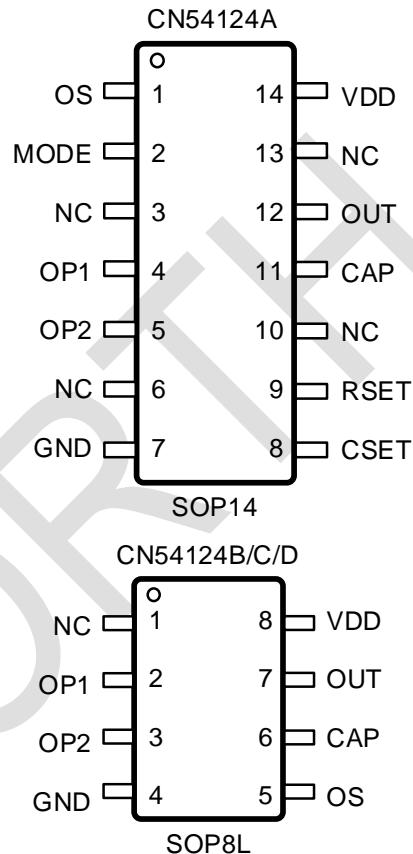

## 4 Pin Configuration

## 5 Ordering Information

| Part NO  | Marking          | Package | Qty/Tape  |

|----------|------------------|---------|-----------|

| CN54124A | CN54124A<br>YYWW | SOP14   | 3000/Tape |

| CN54124B | CN54124B<br>YYWW | SOP8L   | 4000/Tape |

| CN54124C | CN54124C<br>YYWW | SOP8L   | 4000/Tape |

| CN54124D | CN54124D<br>YYWW | SOP8L   | 4000/Tape |

Note: YY=Year WW=Week.

Green (RoHS & HF): CHIPNORTH defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances.

If you have additional comments or questions, please contact your CHIPNORTH representative directly.

Moisture sensitivity level(MSL):3

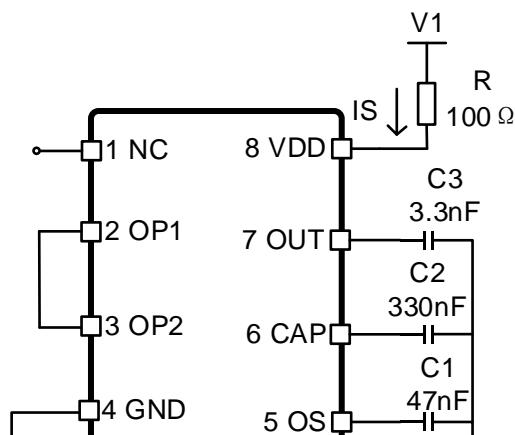

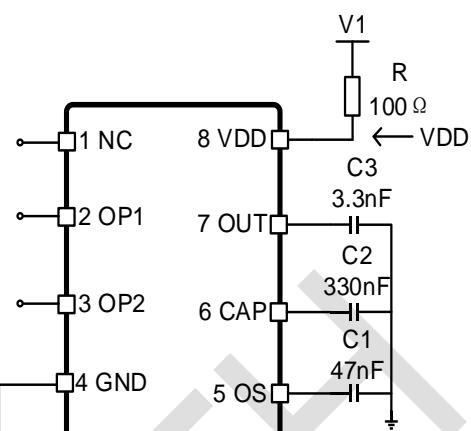

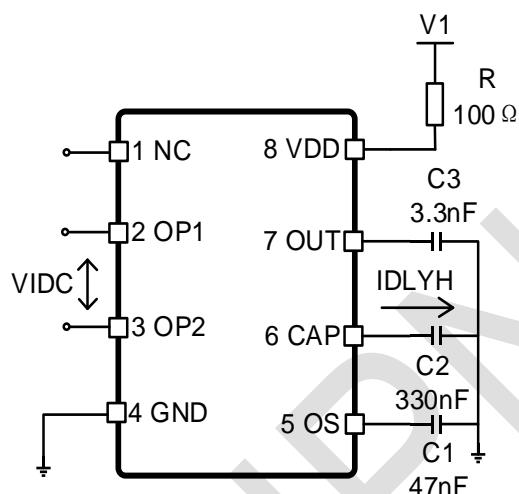

## 6 Typical Application

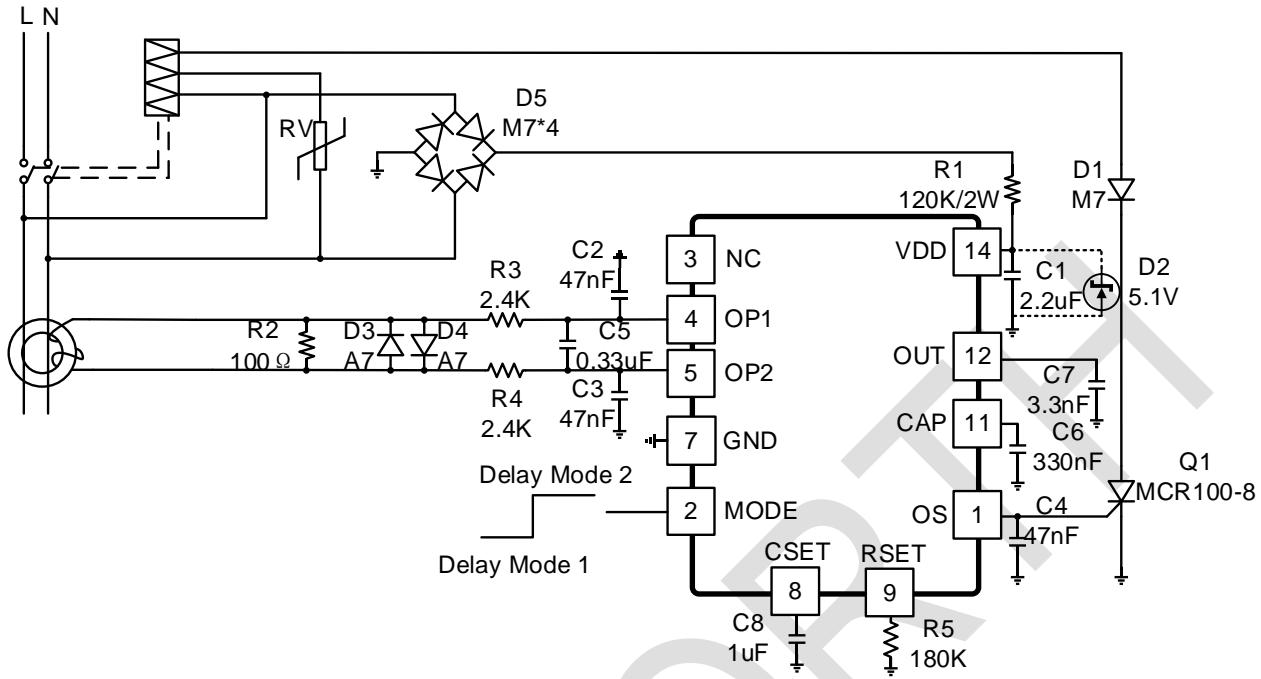

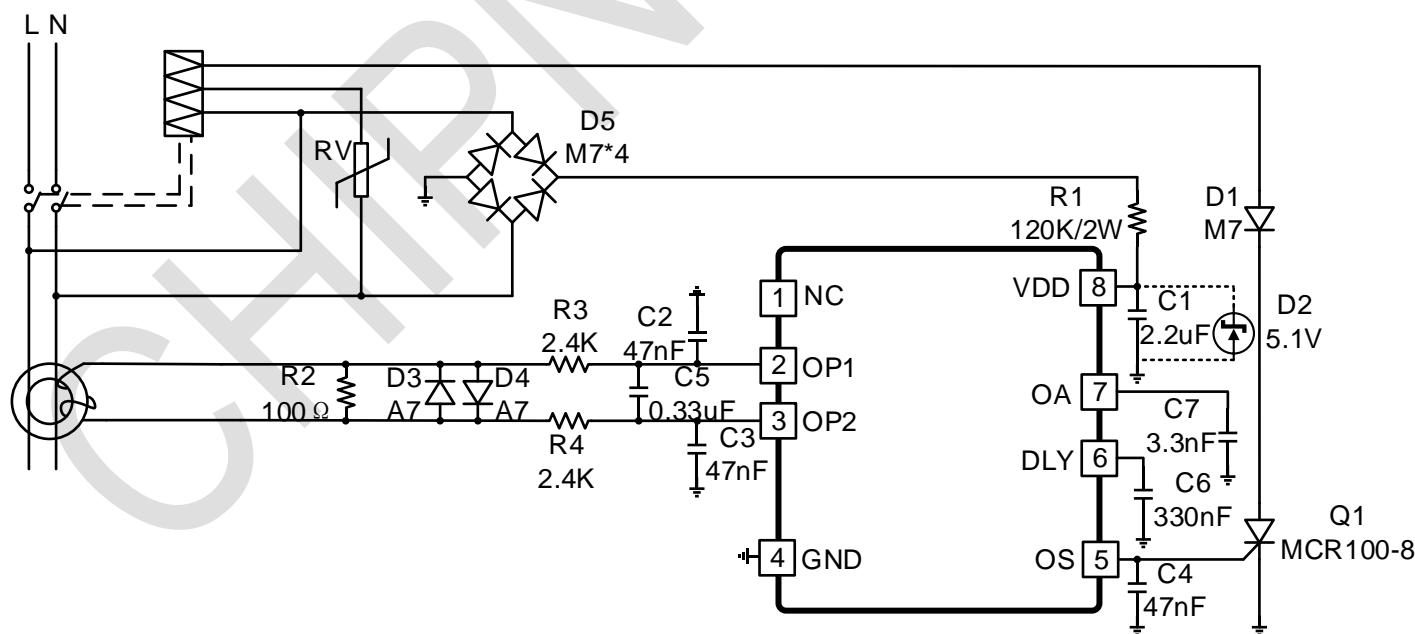

Figure6.1 CN54124A Typical Application

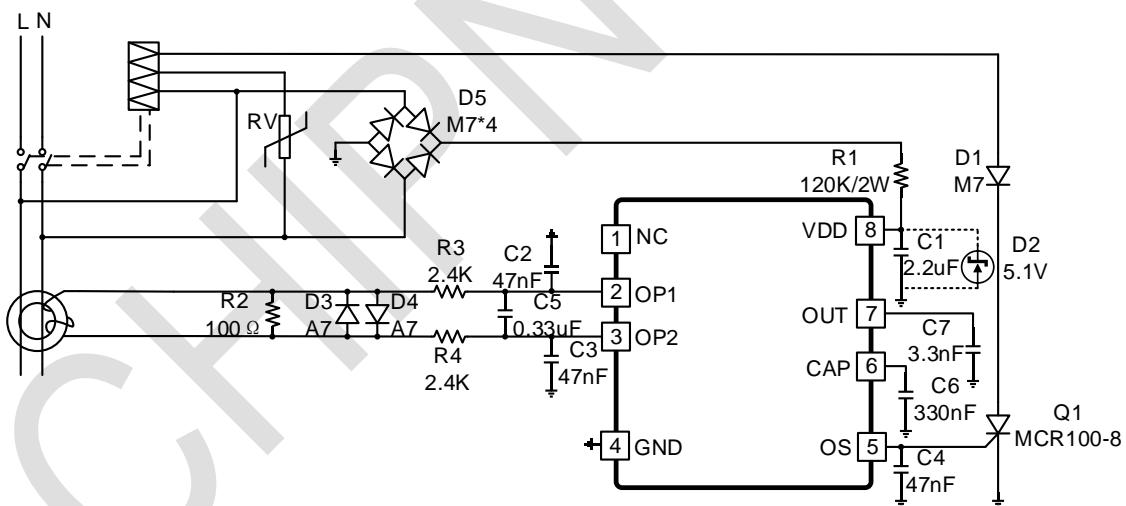

Figure6.2 CN54124B/C/D Typical Application

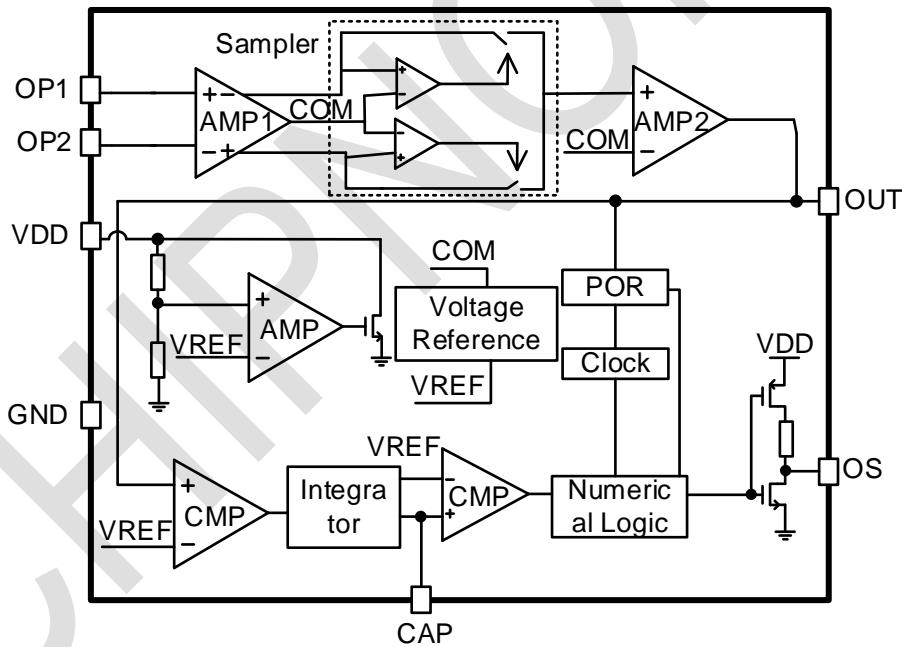

## 7 Block Diagram

Figure 7.1 CN54124A Block Diagram

Figure 7.2 CN54124B Block Diagram

## 8 Pin Descriptions

| Part NO      |              | Pin Name | Descriptions                                                                           |

|--------------|--------------|----------|----------------------------------------------------------------------------------------|

| CN54124A     | CN54124B/C/D |          |                                                                                        |

| 3, 6, 10, 13 | 1            | NC       | No Connect                                                                             |

| 4            | 2            | OP1      | Signal amplifier input 1                                                               |

| 5            | 3            | OP2      | Signal amplifier input 2                                                               |

| 7            | 4            | GND      | Ground                                                                                 |

| 1            | 5            | OS       | Output control SCR                                                                     |

| 11           | 6            | CAP      | Delay setting, connect capacitor                                                       |

| 12           | 7            | OUT      | Amplifier output, connect capacitor                                                    |

| 14           | 8            | VDD      | Power Supply Input                                                                     |

| 9            | N/A          | RSET     | Connect resistor, adjust delay time                                                    |

| 8            | N/A          | CSET     | Connect capacitor, adjust delay time                                                   |

| 2            | N/A          | MODE     | Input, select delay mode.<br>MODE=GND for delay mode 1;<br>MODE=4.5V for delay mode 2. |

## 9 Specifications

### 9.1 Absolute Maximum Ratings

| Parameter                           | Symbol            | Value                | Units |

|-------------------------------------|-------------------|----------------------|-------|

| Operation Voltage                   | VDD               | -0.4~+8              | V     |

| Other Pins                          | VIO               | GND - 0.3, VDD + 0.3 | V     |

| Soldering temperature               | T <sub>LEAD</sub> | 260 (soldering,10s)  | °C    |

| Operating Ambient Temperature Range | T <sub>A</sub>    | -40~+105             | °C    |

| Storage Temperature Range           | T <sub>TG</sub>   | -55~+150             | °C    |

Note\*: Stress exceeds these ratings listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Expose to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 9.2 ESD Ratings

| Discharge mode | Specification               | Value | Units |

|----------------|-----------------------------|-------|-------|

| HBM            | ESDA/JEDEC JS-001-2017      | ±8000 | V     |

| CDM            | ANSI/ESDA/JEDEC JS-002-2022 | ±2000 | V     |

### 9.3 Recommended Operating Range

| Parameter                           | Symbol         | Min. | Max. | Units |

|-------------------------------------|----------------|------|------|-------|

| Operation Voltage                   | VDD            | 3    | 5.5  | V     |

| Operating Ambient Temperature Range | T <sub>A</sub> | -40  | 105  | °C    |

### 9.4 Thermal Information

| Parameter                              | Symbol           | Value | Unit |

|----------------------------------------|------------------|-------|------|

| Junction-to-ambient thermal resistance | R <sub>θJA</sub> | 100   | °C/W |

## 9.5 Electrical Characteristics

( $V_{IN}=4.5V$ ,  $T_A=25^{\circ}C$ , unless otherwise specified.)

| Parameter                  | Symbol | Conditions                          | Test circuit | Min  | Typ  | Max   | Unit |

|----------------------------|--------|-------------------------------------|--------------|------|------|-------|------|

| Quiescent current          | IQ     | $V_{CC}=4.5V$<br>$OP1 - OP2=0mV$    | 1            | 100  | 190  | 280   | uA   |

| Operation Voltage          | VDD    | $I_{VCC}=5mA$                       | 2            | 4.6  | 4.8  | 5     | V    |

| CAP outputs high current   | I_CAPH | $OP1 - OP2=30mV$                    | 3            | 50   | 65   | 80    | uA   |

| CAP outputs low current    | I_CAPL | $OP1 - OP2=0mV$                     | 4            | 1.5  | 2    | 2.5   | uA   |

| OS outputs high current    | I_OSH  | $OP1 - OP2=30mV$ ,<br>CN54124A      | 5            | 1    | 1.7  | 3     | mA   |

|                            |        | $OP1 - OP2=30mV$ ,<br>CN54124B      |              | 0.18 | 0.23 | 0.28  | mA   |

|                            |        | $OP1 - OP2=30mV$ ,<br>CN54124C      |              | 1    | 1.7  | 3     | mA   |

|                            |        | $OP1 - OP2=30mV$ ,<br>CN54124D      |              | 0.18 | 0.23 | 0.28  | mA   |

| OS outputs low voltage     | V_OSL  | $OP1 - OP2=0mV$ ,<br>$I_{OSL}=10mA$ | 6            |      | 0.05 | 0.112 | V    |

| Positive operating voltage | V_PT   | $OP1 - OP2$                         | 7            | 4.65 | 4.95 | 5.35  | mV   |

| Negative operating voltage | V_NT   | $OP2 - OP1$                         | 8            | 4.65 | 4.95 | 5.35  | mV   |

| Latch time                 | TON    | CN54124A                            | 9            | 20   |      |       | mS   |

|                            |        | CN54124B                            |              | 20   |      |       | mS   |

|                            |        | CN54124C                            |              | 20   | 32   | 45    | mS   |

|                            |        | CN54124D                            |              | 20   | 32   | 45    | mS   |

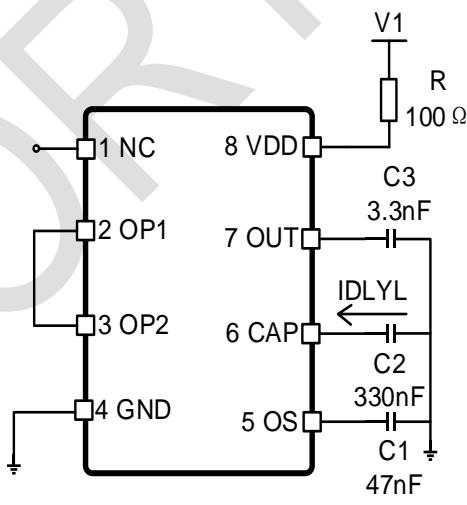

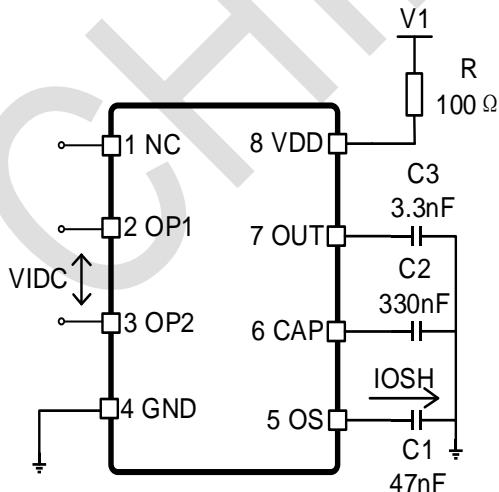

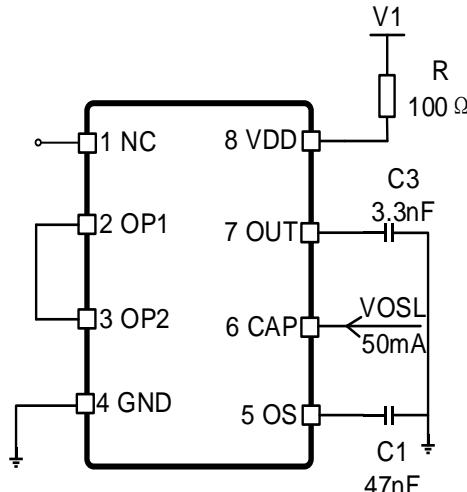

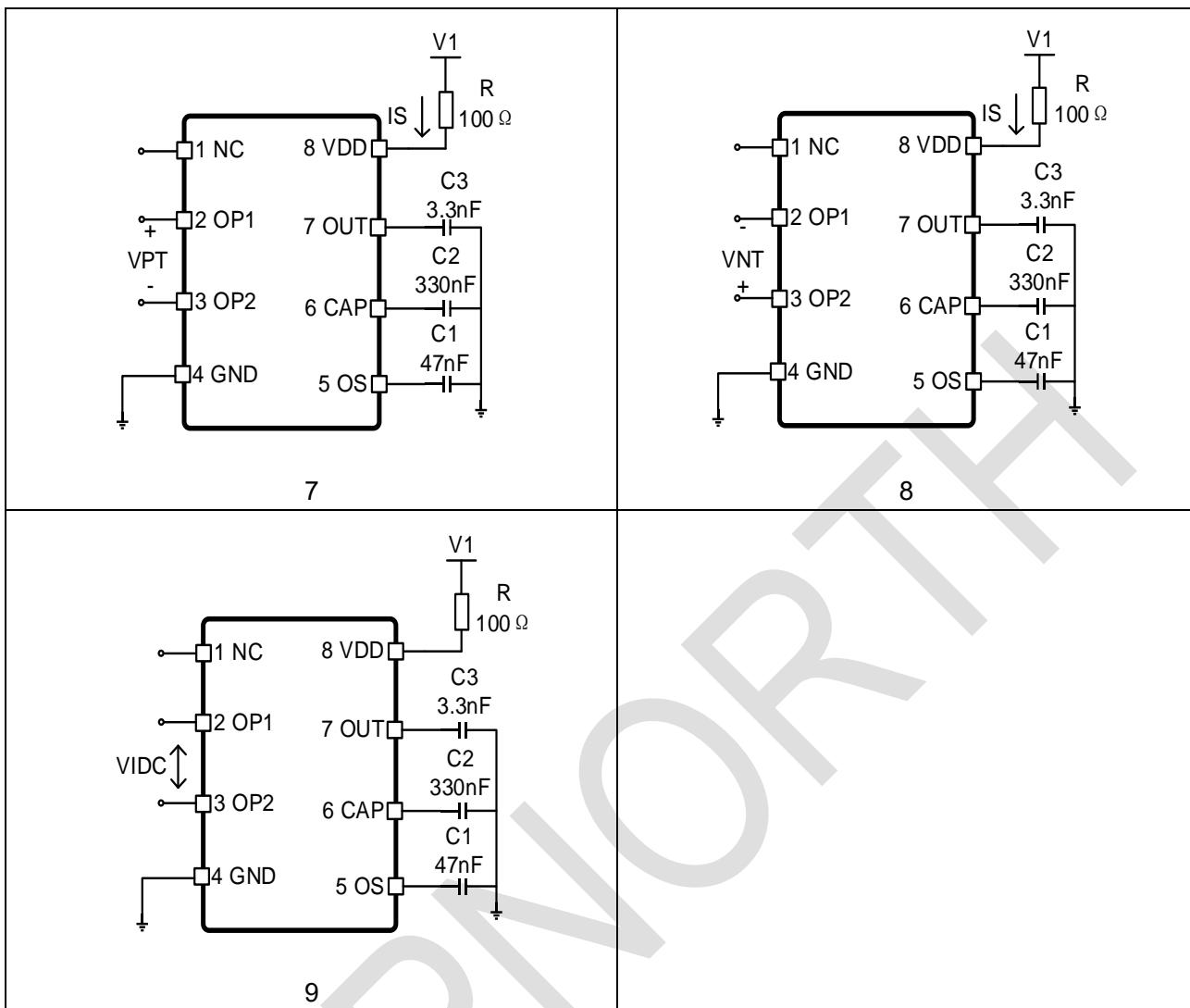

**9.6 Test Circuit**

1

2

3

4

5

6

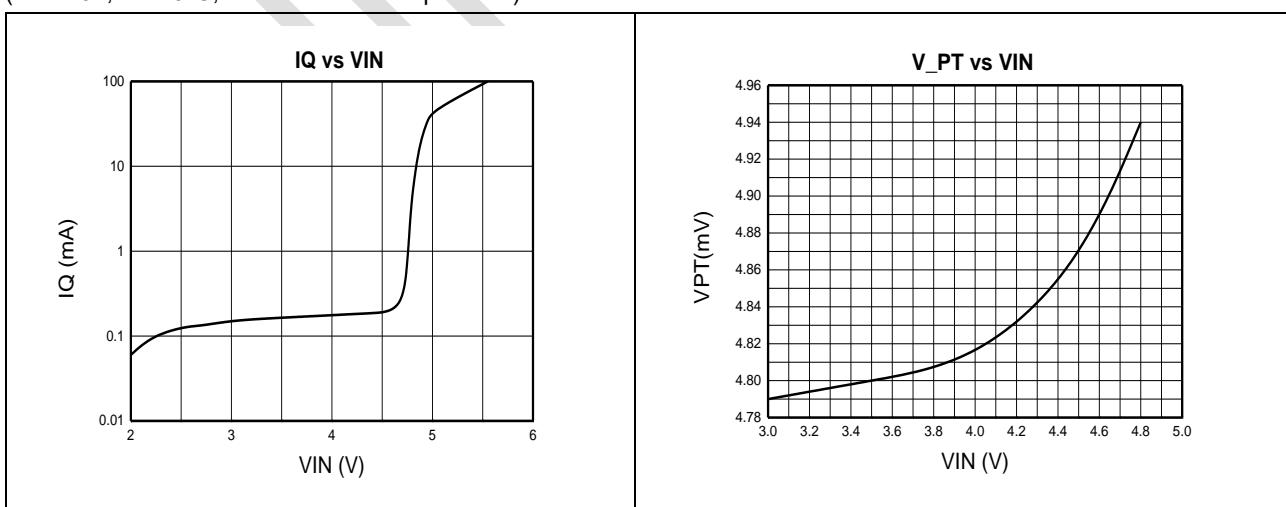

## 9.7 Characteristics Curve

( $V_{IN}=4.5V$ ,  $T_A=25^{\circ}C$ , unless otherwise specified.)

## 10 Detailed Description

The CN54124 is used to detect the leakage on the live and neutral lines. When a leakage signal is generated, the ZCT detects the leakage signal and the secondary coil outputs an inductive signal as the input of the main chip for the Earth leakage circuit breaker. The chip can detect the residual current of type A and type AC. When the RMS value of the leakage current is greater than the rated current (RMS) specified by the Earth leakage circuit breaker, the OS generates an action level with a minimum pulse width of 20ms, which drives the SCR to turn on.

### 10.1 CN54124A Delay Function

When there is a leakage signal and the CAP pin is high, the regulator charges the capacitor outside the CSET pin. The resistor at the RSET terminal (typical value  $R_5 = 180k$ )  $R_5$  provides the reference current  $I_{REF}$  for charging the  $C_8$  capacitor on the CSET pin, and in order to ensure the accuracy of the  $I_{REF}$  current and the corresponding delay time, it is recommended to use a high-precision resistor ( $\pm 2\%$ ).

MODE=0, Delay Mode 1: CSET charging current is  $0.6*VOUT/R_5$ . Delay time correlates with leakage current magnitude—higher leakage results in shorter delay.

MODE=VDD, Delay Mode 2: CSET charging current is  $0.6*VREF/R_5$ . Fixed delay time is set.

The  $I_{REF}$  of MODE=VDD can be calculated by the following formula:

$$I_{REF} = \frac{V_{REF}}{R_5} \times 0.6$$

When the CSET voltage is greater than 1.2V, the OS becomes high and the trip is triggered. The  $T_{delay}$  of MODE=VDD can be calculated by the following formula:

$$T_{delay} = \frac{C_8 \times R_5}{0.6}$$

- $C_8$  is the capacitor connected to the CSET pin,

- $R_5$  is the off-chip high-precision resistor connected to the RSET pin

For example,  $C_8 = 1\mu F$  and  $R_5 = 180K$ , then  $T_{delay} = 300ms$ .

$C_8=1\mu F$ ,  $R_5=1.2M$ , then  $T_{delay}=2s$ .

To ensure that the OS can turn off the driver in a timely manner after the leakage is eliminated, the OUT signal will be detected upon expiration of the latch time (typical 32 ms). If the OUT pin is at a low level, the OS driver will be turned off.

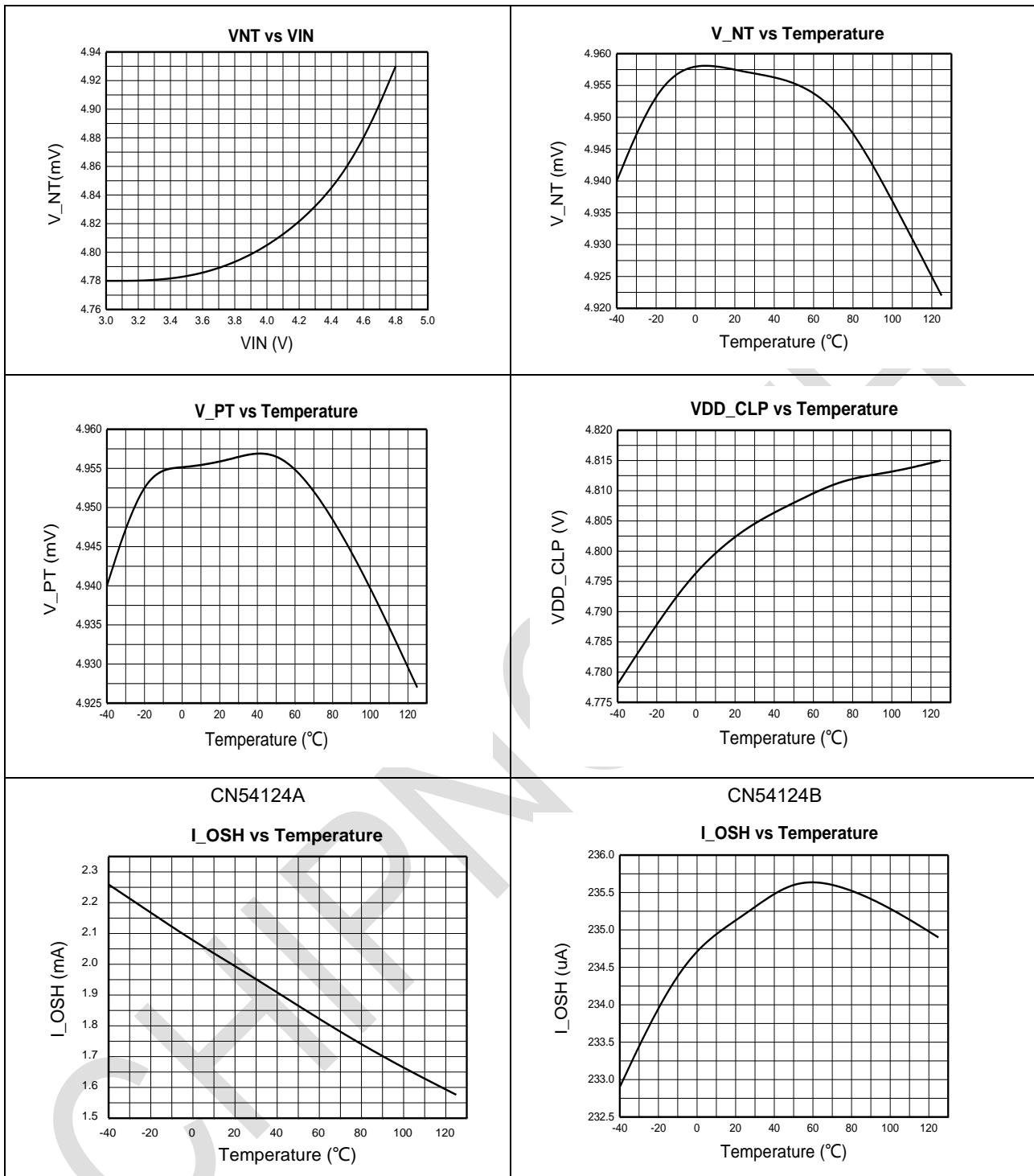

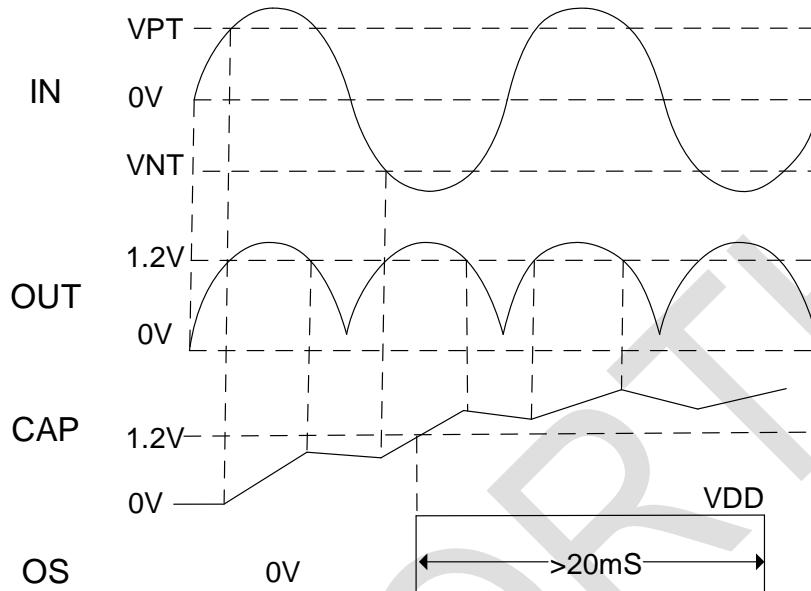

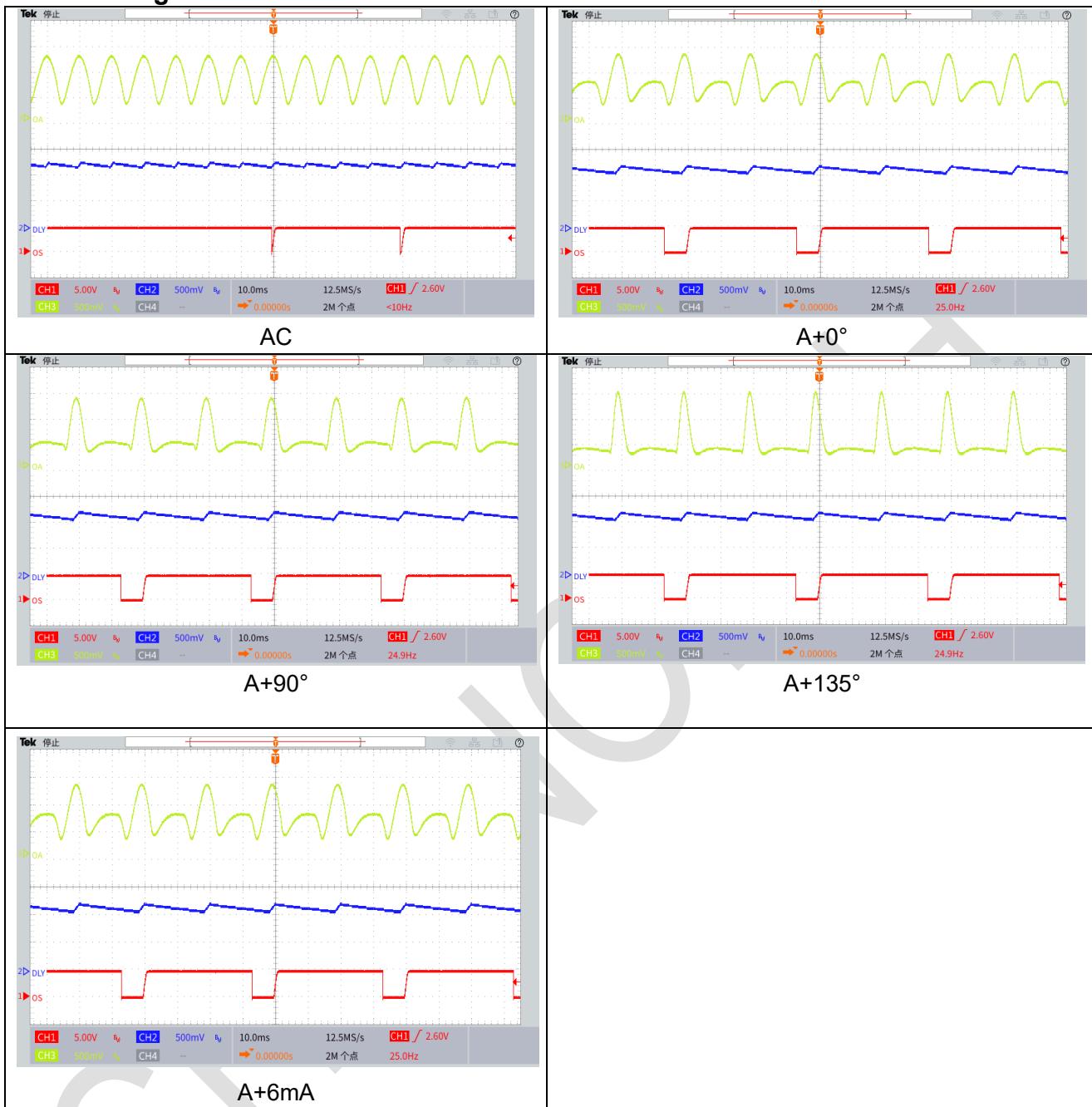

## 10.2 Control Timing

The figure below is an operation diagram of the CN54124B, detecting the leakage signal between OP1 and OP2, when the peak value of the input voltage signal exceeds 4.95mV, the output pin OS generates an action level, and the level pulse width is 20ms minimum, driving the external SCR to turn on.

Figure 5 AC Type Leakage

Figure 6 A+90° Type Leakage

## 11 Application Information

## 11.1 CN54124 Selection Table

| Part NO  | I_OS  | OS output                                                                                                  | Applicable scenarios                                                                                             |

|----------|-------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| CN54124A | 1.7mA | When the leakage current occurs on the L and N lines, the OS outputs pulses until the leakage is removed.  | AC input voltage range: 50V~380V(50/60Hz), full-bridge rectification, A type and AC type leakage                 |

| CN54124B | 0.2mA | When the leakage current occurs on the L and N lines, the OS outputs high until the leakage is removed.    | AC input voltage range: 50V~380V(50/60Hz), half-bridge and full-bridge rectification, A type and AC type leakage |

| CN54124C | 1.7mA | When the leakage current occurs on the L and N lines, the OS outputs a single pulse of at least 20ms.      | AC input voltage range: 50V~380V(50/60Hz), full-bridge rectification, A type and AC type leakage                 |

| CN54124D | 0.2mA | When the leakage current occurs on the L and N lines, the OS outputs only a single pulse of at least 20ms. | AC input voltage range: 50V~380V(50/60Hz), half-bridge and full-bridge rectification, A type and AC type leakage |

## 11.2 Typical Application

The figure below shows a schematic diagram of CN54124B typical application circuit that can be used to evaluate its performance.

In the above application circuit diagram, T0 is the ZCT used to induce the leakage current on the power supply line, R2 is the leakage protection action sensitivity adjustment resistance, the value of the resistance is related to the leakage current required to act and the turn ratio of the ZCT, the action sensitivity inside the CN54124B is 4.95mV, then ideally

$$R_2 = \frac{4.95mV \times n \times k}{\sqrt{2} \times I_{\Delta n}}$$

- $I_{\Delta n}$  is the set threshold current for leakage action

- n is the number of turns of the zero-sequence current transformer T0

- k is the inductance coefficient of the current transformer

R1, C1 and the clamping circuit inside the CN54124B form the power supply circuit, the value of R1 needs to consider the power requirements under the condition of maximum working voltage and the minimum working voltage requirements. Under the condition that the minimum operating voltage is 50 V AC, the maximum clamping current of VDD is 50 mA, considering the heat generation, 120kΩ/2W is recommended for R1 and 2.2uF/50V for C1.

C2 and C3 are common-mode filter capacitors, it is recommended that C2 and C3 use 47nF capacitors. R3 and R4 are current-limiting resistors, and theoretically R3 and R4 are larger to protect the IC, but because the CN54124B uses a voltage amplifier internally, its impedance is limited, so it is recommended that the values of R3 and R4 should not exceed 2.4kΩ. At the same time, R3, R4 and C5 form a low-pass filter circuit, and  $R3 \times C5$  is the frequency retort point (the retort frequency is 1kHz). It is recommended that the value of C5 should not be greater than 330 nF.

C4 filters the high-frequency interference noise that may occur in the circuit breaker, and avoids the false triggering of the SCR Q1 during the power-on process of the circuit breaker.

C6 is the CN54124B delay adjustment capacitor, when the absolute value voltage of the difference between OP1 and OP2 at the input end of the CN54124B is greater than 4.95mV, the output current of the CAP pin of the CN54124B charges C6, and when the voltage of C6 rises to 1.23V, the output of the OS pin of the CN54124B drives the pull-up driving current of the SCR, which is 230uA.

In normal operation, the clamping circuit inside the chip can ensure that the power supply voltage of the chip is below 5V, so as to ensure the normal operation of the chip. However, when a high voltage is directly applied to the power supply pin of the chip when the chip is not working normally (for example, the voltage on the live capacitor C1 is directly applied to the power pin of the chip during the placement process), the chip is at risk of being damaged by the high voltage because the internal clamping circuit has not been started normally. The function of the Zener Diode D2 is to avoid damage to the chip caused by the live capacitor during the production process, and if the selected capacitor C1 has released the residual charge before leaving the factory or before the SMT, the Zener Diode D2 can be omitted.

### 11.3 Working waveform

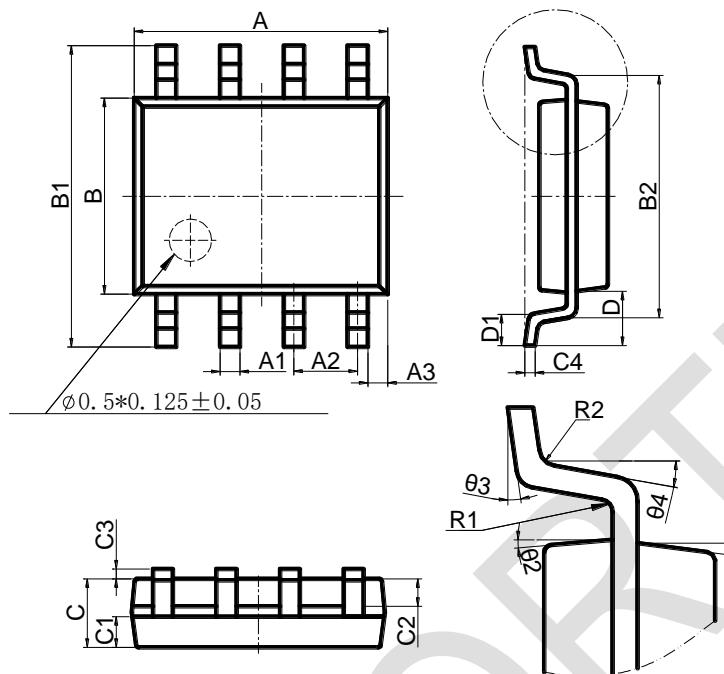

## 12 Package Information

**SOP8L**

| Symbol | MILLIMETER |       | Symbol | MILLIMETER |       |

|--------|------------|-------|--------|------------|-------|

|        | MIN        | MAX   |        | MIN        | MAX   |

| A      | 4.80       | 5.00  | C3     | 0.05       | 0.20  |

| A1     | 0.356      | 0.456 | C4     | 0.203      | 0.233 |

| A2     | 1.27TYP    |       | D      | 1.05TYP    |       |

| A3     | 0.345TYP   |       | D1     | 0.40       | 0.80  |

| B      | 3.80       | 4.00  | R1     | 0.20TYP    |       |

| B1     | 5.80       | 6.20  | R2     | 0.20TYP    |       |

| B2     | 5.00TYP    |       | θ1     | 17°TYP4    |       |

| C      | 1.30       | θ2    | θ2     | 13°TYP4    |       |

| C1     | 0.55       | 0.65  | θ3     | 0°~8°      |       |

| C2     | 0.55       | 0.65  | θ4     | 4°~12°     |       |

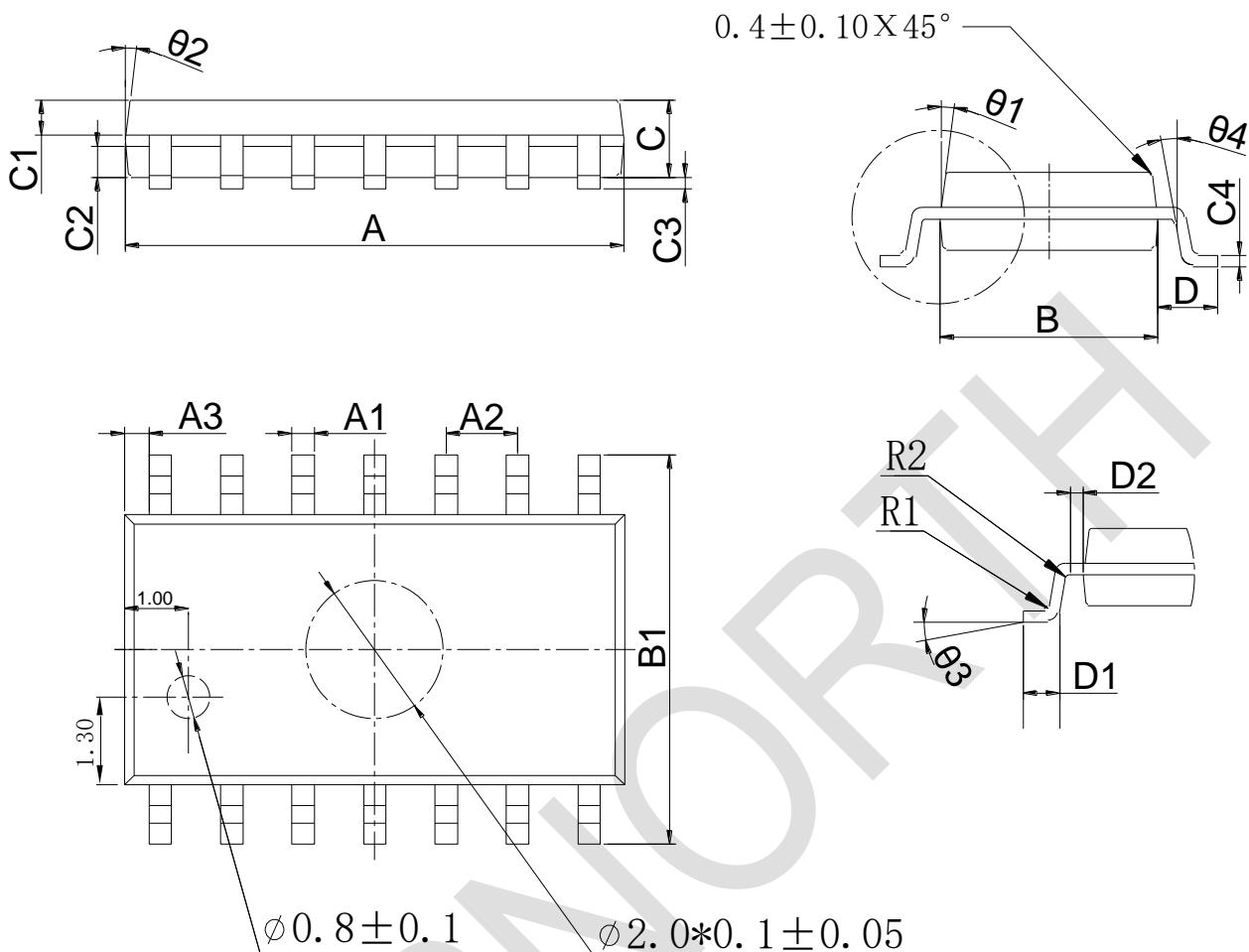

**SOP14**

| Symbol | MILLIMETER |       | Symbol | MILLIMETER  |       |

|--------|------------|-------|--------|-------------|-------|

|        | MIN        | MAX   |        | MIN         | MAX   |

| A      | 8.55       | 8.75  | C4     | 0.193       | 0.213 |

| A1     | 0.356      | 0.456 | D      | 0.95        | 1.15  |

| A2     | 1.27TYP    |       | D1     | 0.40        | 0.70  |

| A3     | 0.312TYP   |       | D2     | 0.20TYP     |       |

| B      | 3.80       | 4.00  | R1     | 0.20TYP     |       |

| B1     | 5.80       | 6.20  | R2     | 0.20TYP     |       |

| C      | 1.40       | 1.60  | θ1     | 8°~12° TYP4 |       |

| C1     | 0.60       | 0.70  | θ2     | 8°~12° TYP4 |       |

| C2     | 0.55       | 0.65  | θ3     | 0°~8°       |       |

| C3     | 0.05       | 0.25  | θ4     | 4°~12°      |       |

## 13 Important Statement

Chipnorth Electronic Technology (Nanjing) Co., Ltd. and its subsidiaries reserve the right to make modifications, improvements, corrections, or other changes to this document and to any of the products described herein at any time without notice. Chipnorth Electronic Technology (Nanjing) Co., Ltd. disclaims any liability arising out of the use of this document or any of the products described herein; Chipnorth Electronic Technology (Nanjing) Co., Ltd. does not transfer any license to its patents or trademarks or other rights. Any customer or user using this document or any of the products described herein assumes all risk and agrees to hold harmless Chipnorth Electronic Technology (Nanjing) Co., Ltd. and all companies whose products are displayed on Chipnorth Electronic Technology (Nanjing) Co., Ltd.

Chipnorth Electronic Technology (Nanjing) Co., Ltd. makes no warranty and assumes no responsibility for any products purchased through unauthorized sales channels. In the event that a customer purchases or uses a product from Chipnorth Electronic Technology (Nanjing) Co., Ltd. for any unintended or unauthorized use, the customer shall indemnify and hold harmless Chipnorth Electronic Technology (Nanjing) Co., Ltd. and its representatives from and against all claims, damages, and attorney's fees arising from any personal injury or death, directly or indirectly, arising out of or in connection with such purchase or use.