# Low Standby-Power AC/DC Converter

### 1 Description

CN1102AC/D/E/F is a highly performance AC/DC converter for wide voltage input, which integrates a PWM controller and 1000V MOSFET with high voltage startup to achieve ultra-low standby power consumption. CN1102AC/D/E/F adopts hybrid PWM/PFM/Burst modulation technology which ensures optimal system efficiency over the full load range, and also integrates frequency dithering technology to simplify system EMI design. CN1102AC/D/E/F provides excellent protection functions, including cycle-by-cycle overcurrent protection, CS resistor short-circuit protection, VDD over voltage protection, overload protection, output short-circuit protection, open feedback protection and over temperature protection.

#### 2 Features

- Built-in 1000V MOSFET

- Built-in high-voltage starting circuit

- Built-in line voltage compensation and slope compensation

- Integrated frequency expansion technology

- Frequency tripling function to improve magnetic interference (Available in CN1102AD/F)

- Integrated input undervoltage protection (Available in CN1102AE/F)

- Integrated short-circuit protection for the primary main winding of the transformer

- PWM/PFM/Burst hybrid control mode

- No-load power consumption <50mW</li>

@230 VAC

- Complete protection functions (OCP, OLP, UVLO, VDD OVP, OTP)

#### 3 Applications

- Switching power supply

- Smart Meter

#### 4 Ordering information

| Product Code | Package | Quantity/Tape |

|--------------|---------|---------------|

| CN1102ACUFU  | DIP-7   | 50/Tape       |

| CN1102ADUFU  | DIP-7   | 50/Tape       |

| CN1102ADSHR  | SOP-8   | 100/Tape      |

| CN1102AEUFU  | DIP-7   | 50/Tape       |

| CN1102AFUFU  | DIP-7   | 50/Tape       |

#### 5 Marking

| Product Code   | Marking  |

|----------------|----------|

| CN1102ACUFU    | CN1102AC |

| CNTTOZACOFO    | YYWW     |

| CN1102ADUFU    | CN1102AD |

| CNTIUZADUFU    | YYWW     |

| CN1100ADCHD    | CN1102AD |

| CN1102ADSHR    | YYWW     |

| CNI4402AELIELI | CN1102AE |

| CN1102AEUFU    | YYWW     |

| CN1102AFUFU    | CN1102AF |

| CIVITIOZAPOPO  | YYWW     |

Note: YY=Year; WW=Week

Green (RoHS & HF): CHIPNORTH defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your CHIPNORTH representative directly. Moisture sensitivity level (MSL): 3

#### **6 Model Description**

| Product Model | Function                           |

|---------------|------------------------------------|

| CN1102AC      | No anti-magnetic function          |

| CNTTUZAC      | No input undervoltage protection   |

| CN1102AD      | With anti-magnetic function        |

| CNTTUZAD      | No input undervoltage protection   |

| CN1102AF      | No anti-magnetic function          |

| CNTTUZAE      | With input undervoltage protection |

| CNI4400AF     | With anti-magnetic function        |

| CN1102AF      | With input undervoltage protection |

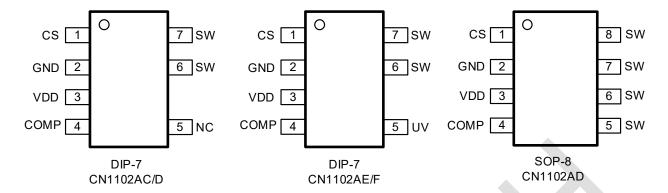

#### 7 Pinout

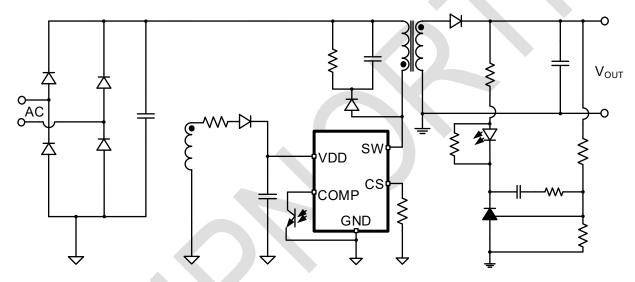

# **8 Typical Application**

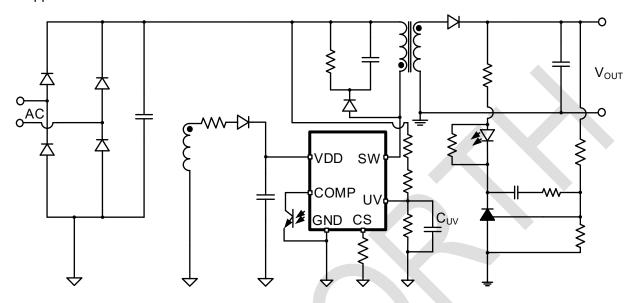

Typical Application Diagram of CN1102AC, CN1102AD

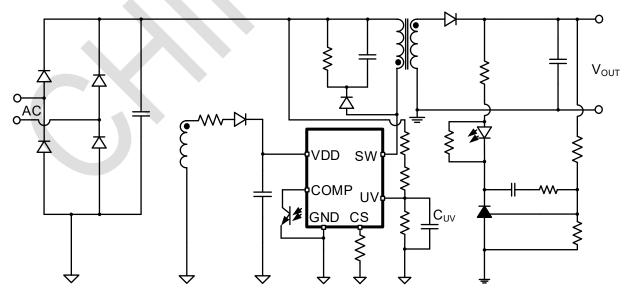

Typical Application Diagram of CN1102AE, CN1102AF

Note: The recommended  $C_{\text{UV}}$  value is about 10nF

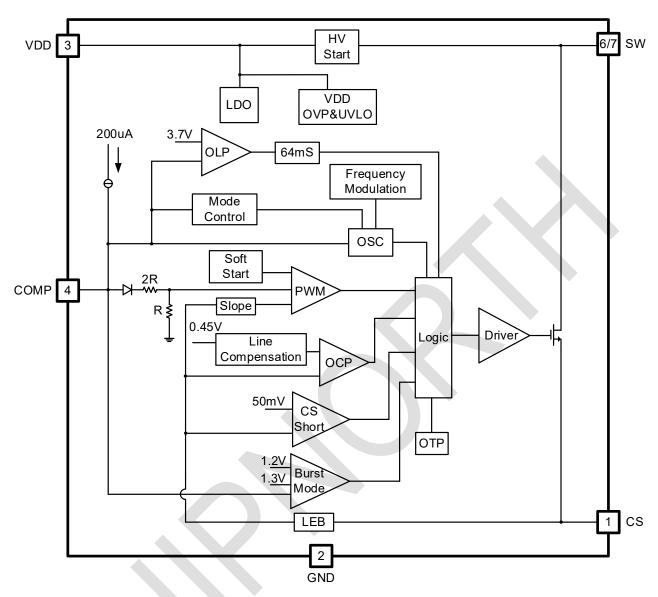

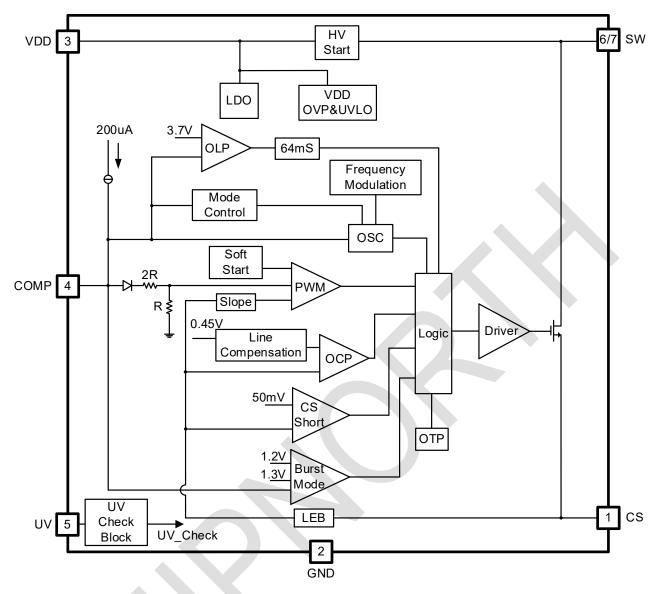

## 9 Block Diagram

Functional Block Diagram of CN1102AC, CN1102AD

Note: The SW pin in SOP-8 package is 5/6/7/8.

Functional Block Diagram of CN1102AE, CN1102AF

# **10 Pin Descriptions**

| Pin    | Pin No. | Pin No. |                                                                                  |

|--------|---------|---------|----------------------------------------------------------------------------------|

| Name   | (DIP-7) | (SOP-8) | Descriptions                                                                     |

| CS     | 1       | 1       | Built-in high voltage MOSFET source pin, current sense pin                       |

| GND    | 2       | 2       | Ground                                                                           |

| VDD    | 3       | 3       | Operating voltage input pin                                                      |

| COMP   | 4       | 4       | Feedback pin                                                                     |

| NC/UV  | 5       | ,       | NC: No connection (only available in CN1102AC/D)                                 |

| INC/UV | 5       | /       | UV: Input undervoltage protection detection pin (only available in CN1102AE/F)   |

| SW     | 6/7     | 5/6/7/8 | Built-in high-voltage MOSFET drain pin, connected to transformer primary winding |

## 11 Specifications

## 11.1 Absolute Maximum Ratings

| Parameter                          | Value               | Units |

|------------------------------------|---------------------|-------|

| VDD pin withstand voltage          | 36                  | V     |

| SW pin withstand voltage           | 1000                | V     |

| Ambient temperature                | -40~105             | °C    |

| Soldering Temperature              | 260 (soldering,10s) | °C    |

| Storage Temperature Range          | -55~150             | °C    |

| Drain pulse current (Tpulse=100us) | 2                   | Α     |

Note: The limit parameter is a threshold that can't be exceeded under any condition (even an instant). Once the chip runs beyond the limit parameters, it may cause aging or permanent damage. The limit parameter only emphasizes numerical values and does not necessarily indicate that the chip can work properly under these limits.

## 11.2 ESD Ratings

| Discharge mode | Value | Units |

|----------------|-------|-------|

| НВМ            | ±4000 | V     |

| CDM            | ±2000 | V     |

# 11.3 Typical Output Power

| Package | Input Voltage Range | Open Average Power | Open Peak Power |

|---------|---------------------|--------------------|-----------------|

| DIP-7   | 85-425Vac           | 10W                | 13W             |

| DIF-1   | 230V±15%            | 13W                | 18W             |

#### 11.4 Thermal Information

| Package | Parameter        | Descriptions        | Value | Unit |

|---------|------------------|---------------------|-------|------|

| DIP-7   | Rθ <sub>JA</sub> | Junction to ambient | 80    | °C/W |

| DIP-1   | Rθ <sub>JC</sub> | Junction to case    | 40    | °C/W |

| SOP-8   | Rθ <sub>JA</sub> | Junction to ambient | 110   | °C/W |

| 30P-0   | Rθ <sub>JC</sub> | Junction to case    | 80    | °C/W |

## 11.5 Electrical Characteristics

Test conditions: TA=25°C, VDD=15V, unless otherwise specified.

| Parameter                       | Symbol Conditions         |                                                                            |       | Value    |       | Unit  |

|---------------------------------|---------------------------|----------------------------------------------------------------------------|-------|----------|-------|-------|

| Parameter                       |                           |                                                                            | Min   | Тур      | Max   | Oilit |

| Chip Power Supply Section       |                           |                                                                            |       |          |       |       |

| Starting Voltage                | V <sub>SW_START</sub>     |                                                                            |       |          | 55    | V     |

| Startup Charging Current        | I <sub>DD_CH</sub>        | V <sub>SW</sub> =105V, V <sub>COMP</sub> =GND,                             |       | 1.5      |       | mA    |

|                                 |                           | V <sub>DD</sub> =10V                                                       |       |          |       |       |

| Operating Voltage Range         | V <sub>DD</sub>           | After turn-on                                                              | 9     |          | 28    | V     |

| VDD Over-Voltage Protection     | V <sub>DDOVP</sub>        | V <sub>CS</sub> =0V, V <sub>COMP</sub> =2V,  Ramp up VDD until gate is off | 28    | 30       | 32    | V     |

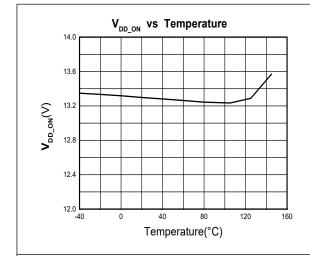

|                                 | V <sub>DDON</sub>         | V <sub>COMP</sub> =GND                                                     | 12    | 13       | 14    | V     |

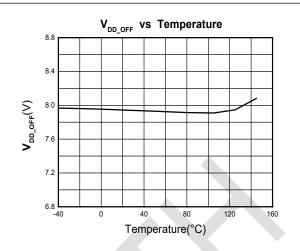

| UVLO Threshold Voltage          | V <sub>DDOFF</sub>        | V <sub>COMP</sub> =GND                                                     | 7.5   | 8        | 8.5   | V     |

| Quiescent Current               | I <sub>DD0</sub>          | V <sub>DD</sub> =15V, V <sub>COMP</sub> =GND                               |       | 0.8      | 1.2   | mA    |

| Operating Current               | I <sub>DD1</sub>          | V <sub>DD</sub> =15V, V <sub>COMP</sub> =2V                                |       | 1.5      | 2     | mA    |

| Protection Mode Current         | I <sub>DD_FAULT</sub>     |                                                                            |       | 170      | 220   | uA    |

| Under-Voltage Working Current   | I <sub>DD_OFF</sub>       | V <sub>DD</sub> =6V                                                        |       | 100      | 130   | uA    |

| COMP Section                    |                           |                                                                            |       |          |       |       |

| Open Loop Voltage               | V <sub>COMP_OPEN</sub>    |                                                                            |       | 4.8      |       | V     |

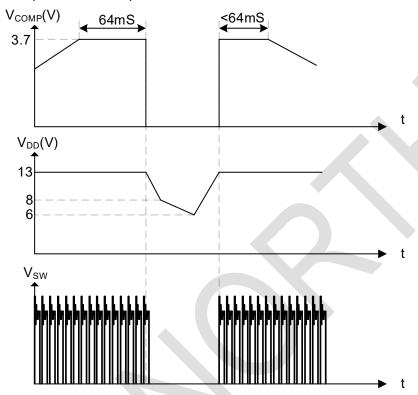

| Overload Protection Threshold   | V <sub>COMP_OLP</sub>     |                                                                            |       | 3.7      |       | V     |

| Anti-magnetic Mode Threshold    | - GOINI _GEI              |                                                                            |       |          |       | -     |

| (Available in CN1102AD/F)       | V <sub>COMP_TRI</sub>     |                                                                            |       | 3.0      |       | V     |

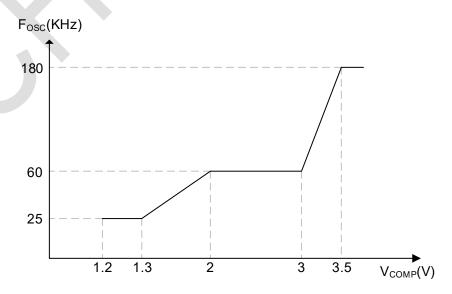

|                                 | V <sub>COMP_PFM</sub>     | Voltage falling when                                                       |       |          |       |       |

| PFM Operating Mode Threshold    |                           | frequency decrease                                                         |       | 2.0      |       | V     |

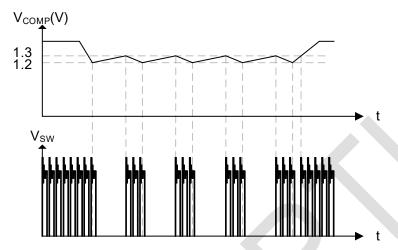

| Burst Mode Threshold            | V <sub>COMP_BM</sub>      | Voltage falling                                                            |       | 1.2      |       | V     |

| Burst Mode Hysteresis Threshold | V <sub>COMP_BM_HYS</sub>  | Voltage rising                                                             |       | 1.3      |       | V     |

| COMP Short Circuit Current      | ICOMP                     | V <sub>COMP</sub> =GND                                                     |       | -200     |       | uA    |

| Overload Protection Delay Time  | T <sub>D_OLP</sub>        |                                                                            |       | 64       |       | mS    |

| Detection Voltage Gain          | A <sub>VCS</sub>          |                                                                            |       | 3.3      |       | V/V   |

| Current Detection Section       |                           |                                                                            |       |          |       |       |

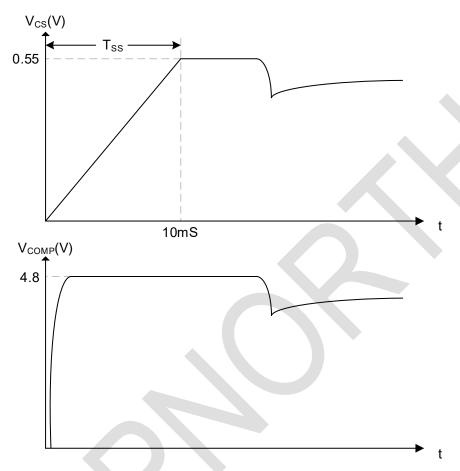

| Soft Start Time                 | T <sub>SS</sub>           |                                                                            |       | 10       |       | mS    |

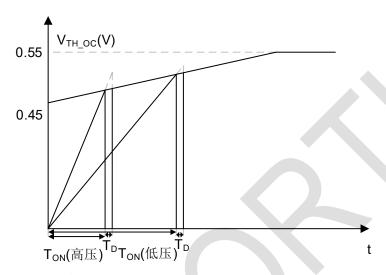

| Minimum T <sub>ON</sub>         | T <sub>ON MIN</sub>       |                                                                            |       | 400      |       | nS    |

| Turn Off Delay Time             | T <sub>D</sub>            |                                                                            |       | 150      |       | nS    |

| Leading-Edge Blanking Time      | T <sub>LEB</sub>          |                                                                            |       | 350      |       | nS    |

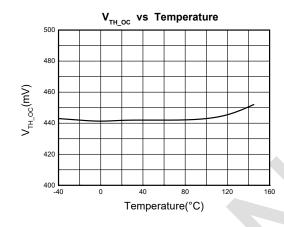

| CS Limit Threshold              | V <sub>TH_OC</sub>        |                                                                            | 0.425 | 0.45     | 0.475 | V     |

| CS Clamp Voltage                | V <sub>OCP_CLAMPING</sub> |                                                                            |       | 0.55     |       | V     |

| Built-in Oscillator Section     | JOI _GEAWN NAG            |                                                                            | 1     |          | 1     | l     |

| Maximum Switching Frequency     |                           |                                                                            |       |          |       |       |

| (Available in CN1102AD/F)       | F <sub>OSC_MAX</sub>      |                                                                            | 162   | 180      | 198   | KHz   |

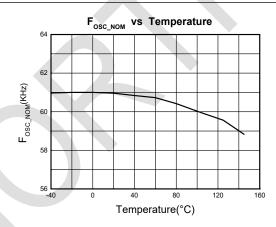

| Switching Frequency             | Fosc                      | VDD in operating voltage range, V <sub>COMP</sub> =2V                      | 54    | 60       | 66    | KHz   |

| Frequency Jitter Range          | F <sub>D</sub>            |                                                                            |       | ±5       |       | KHz   |

| Modulation Frequency            | F <sub>M</sub>            |                                                                            |       | 250      |       | Hz    |

|                                 | 1                         | 1                                                                          | 1     | <u> </u> | 1     |       |

| Maximum Duty Cycle             | D <sub>MAX</sub>    |                                              | 70   |      | 85   | %   |

|--------------------------------|---------------------|----------------------------------------------|------|------|------|-----|

| Burst-Mode Frequency           | F <sub>Burst</sub>  |                                              | 21.5 | 25   |      | KHz |

| UV Detection Section           |                     |                                              |      |      |      |     |

| Pull-up current                | I <sub>UV</sub>     |                                              |      | 1    |      | uA  |

| Clamp Voltage                  | V <sub>UV_CLP</sub> | I_UV=0.5mA                                   |      | 5    |      | V   |

| Detection Threshold Voltage    | V <sub>UV_REF</sub> |                                              | 0.52 | 0.55 | 0.58 | V   |

| Over-Temperature Protection Se | ction               |                                              |      |      |      |     |

| Over-Temperature Protection    | T <sub>SD</sub>     |                                              | 135  | 150  |      | °C  |

| Over-Temperature Protection    | т                   |                                              |      | 30   |      | °C  |

| Hysteresis                     | T <sub>HYST</sub>   |                                              |      | 30   |      |     |

| Built-In MOSFET Section        |                     |                                              |      |      |      |     |

| Drain-Source Breakdown Voltage | BV <sub>DSS</sub>   | I <sub>SW</sub> =250uA, T <sub>J</sub> =25°C | 1000 |      |      | V   |

| MOSFET On-Resistance           | R <sub>DS_ON</sub>  | I <sub>SW</sub> =0.5A, T <sub>J</sub> =25°C  |      |      | 10   | Ω   |

## 11.6 Characteristic Curve

#### 12 Detailed Description

#### 12.1 Overview

CN1102AC/D/E/F is an efficient switching power supply controller integrating power MOSFET and PWM controller, and the extremely compact peripheral components make it easier to design switching power supplies. CN1102AC/D/E/F provides extremely complete and intelligent protection functions, including cycle-by-cycle overload protection, over-voltage protection, CS resistor short circuit protection, overtemperature protection and soft-start function, etc. In addition, the hybrid modulation technique of PWM, PFM and Burst can realize the best performance of the system under different loads; and the unique high-voltage start-up design can realize lower standby power consumption. The built-in frequency dithering function and frequency modulation technology enable better EMI performance, and the CN1102AC/D/E/F provides a reliable solution for ultra-low standby power applications.

# **12.2 Functional Description**

# **12.2.1 Startup**

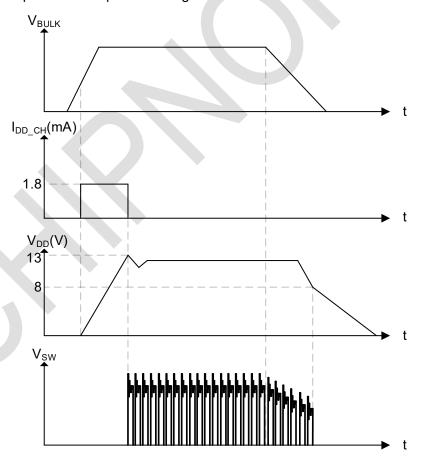

The built-in high voltage starter MOS provides 1.5 mA current to charge the external VDD capacitor. Once the VDD voltage reaches 13V, CN1102AC/D/E/F starts to work immediately, at this time the high voltage starter MOS will stop charging the VDD capacitor, the VDD capacitor discharges to maintain the chip working, the VDD voltage drops slightly, then the transformer auxiliary winding provides energy to the VDD capacitor to keep the VDD capacitor voltage stable.

#### 12.2.2 Soft Start

During the start-up phase, the limit value of the maximum peak current at the drain of the built-in power MOS is slowly raised; this minimizes the stress on the device and prevents transformer saturation. The soft-start time of CN1102AC/D/E/F is typically 10ms.

#### 12.2.3 Output Driver

CN1102AC/D/E/F adopts unique driving technology and optimizes the totem pole structure to reasonably configure the driving current and dead time, resulting in better EMI performance and lower loss.

#### 12.2.4 Oscillator

CN1102AC/D/E/F does not require peripheral circuitry for frequency setting, the built-in oscillator frequency is fixed at 60KHz, equipped with a unique frequency dithering technology, which can further optimize the EMI characteristics.

#### 12.2.5 Feedback Control

The chip adopts the current mode control technology, the voltage of COMP pin can control the current of the power MOS, so as to achieve the purpose of voltage regulation.

#### 12.2.6 Burst Operation Mode

Under light load, CN1102AC/D/E/F will operate in Burst mode to reduce system power consumption. When the load is lightened, the COMP pin voltage decreases and the chip enters the Burst operation mode when  $V_{\text{COMP}}$  is less than the Burst mode threshold (typically 1.2V). Once  $V_{\text{COMP}}$  exceeds the Burst mode hysteresis threshold, CN1102AC/D/E/F can exit Burst mode.

#### 12.2.7 PFM Operation Mode

CN1102AC/D/E/F provides a PFM operation mode, which detects the COMP pin voltage and reduces the switching frequency under light load and no-load conditions to improve the light load efficiency. When the COMP pin voltage is less than 2V, the chip enters the PFM operation mode, and the minimum frequency of this chip is 25KHz, where the switching frequency decreases with the load, to eliminate noise under light load conditions.

#### 12.2.8 PWM Operation Mode

When CN1102AC/D/E/F operates in the heavy load  $V_{COMP}$  greater than 2V condition, it enters the PWM operation mode and the operating frequency is kept constant at 60KHz.

#### 12.2.9 Frequency Ascension Mode (Available in CN1102AD/F)

When CN1102AD/F operates under strong magnetic or overload  $V_{\text{COMP}}$  greater than 3V, it will enter the frequency ascension mode, and the operating frequency will be linearly increased to 3 times of the original with  $V_{\text{COMP}}$  to compensate for the effect of the transformer inductance decreasing under the strong magnetic field.

#### 12.2.10 Overload Protection

When the load current exceeds the preset value, the system will enter the overload protection ("hiccup" type protection): it can protect the system under abnormal conditions. When the  $V_{COMP}$  pin voltage exceeds 3.7V and after a fixed delay of 64ms, the chip will enter the overload protection, and after the fault is removed, the chip can resume operation.

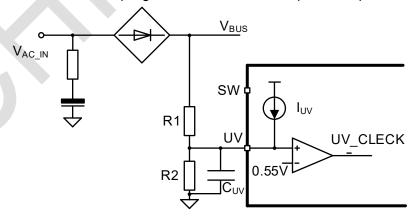

#### 12.2.11 Input undervoltage protection (Available in CN1102AE/F)

CN1102AE/F integrates an input voltage detection module, from the input filter capacitor, through the voltage divider resistor connected to UV pin, the system will detect the UV voltage after startup and compare it with the internal reference, when the UV voltage is greater than 0.55V, the system will start to work, if UV voltage is lower than 0.55V, it will stop working. UV pin needs to be connected to a filter capacitor of 10nF to attenuate the coupling interference of the SW pin to UV pin.

The input starting voltage V<sub>AC IN</sub> is calculated as follows:

$$V_{AC\_IN} = \frac{1}{1.414} \times \left( \frac{0.55}{R2} - I_{UV} \right) \times (R1 + R2)$$

R1 and R2 are in  $K\Omega$  and  $I_{UV}$  is in mA.

#### 12.2.12 Line Voltage Compensation

CN1102AC/D/E/F provides overcurrent line voltage compensation to achieve constant output power limitation over the full voltage range.T<sub>D</sub> is the conduction delay time. Under high voltage conditions, the turn-on time is shorter compared to low voltage conditions. After line voltage compensation, the VTH\_OC is lower during high voltage input, but the current sampling value at the CS pin during the TD period is higher. These two factors collectively result in a consistent peak current level under both high and low voltage inputs

#### 12.2.13 Ramp Compensation

CN1102AC/D/E/F provides ramp compensation, which superimposes a voltage sawtooth signal on the sampled current signal and is used to improve the stability of the system loop.

#### **12.2.14 Overcurrent Protection**

CN1102AC/D/E/F has cycle-by-cycle overcurrent protection. The current flowing through MOSFET can be detected and controlled by setting the resistor between the CS pin and GND to adjust the overcurrent protection value.

#### 12.2.15 CS Resistor Short Circuit Protection

CN1102AC/D/E/F provides CS resistor short circuit protection. If the CS resistor is short-circuited before the system starts up, the chip enters the CS resistor short-circuit protection state. It can protect the system under abnormal conditions.

#### 12.2.16 Transformer primary short-circuit protection

CN1102AC/D/E/F provides transformer primary short circuit protection. If the transformer primary main winding is short-circuited before the system starts up, the chip enters the protection state. Under abnormal conditions, the system can be protected.

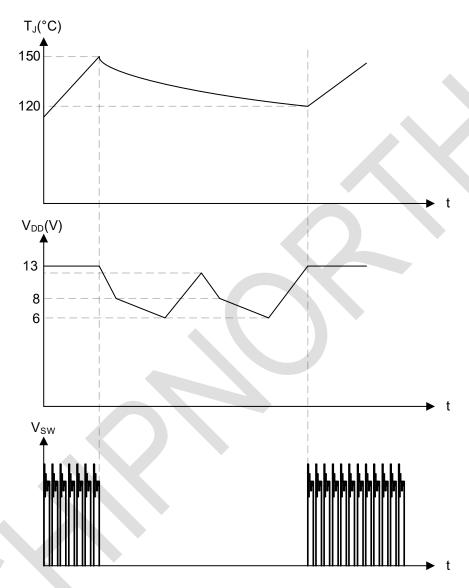

## 12.2.17 Over Temperature Protection

The power MOSFET and the control circuit are integrated together, making it easier for the control circuit to detect the temperature of the MOSFET. When the temperature exceeds 150°C, the chip enters the over-temperature protection state; when the temperature recovers to 120°C, the chip can resume operation.

## 13 Application Information

#### 13.1 Typical Application

The following figure shows the schematic of a typical application circuit that can be used as a means of evaluating the performance of CN1102AC/D/E/F. This section describes the design process specific to the application schematic.

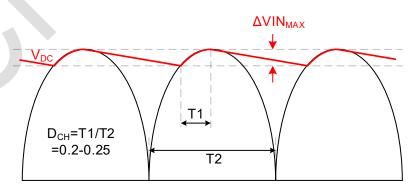

## 13.2 Selection of Input Capacitor

$$C_{BUS} = \frac{P_{IN} \times (1 - D_{CH})}{\sqrt{2} \times VAC_{MIN} \times 2 \times f_L \times \Delta VIN_{MAX}}$$

- Input Power P<sub>IN</sub>=P<sub>O</sub>/η (η is the efficiency)

- VAC<sub>MIN</sub> is the minimum AC input voltage

- f<sub>L</sub> is the line AC frequency, generally 50~60Hz

- D<sub>CH</sub> is the duty cycle, its typical value is 0.2~0.3

General  $\Delta VIN_{MAX}$  is set as 10%~30% of  $\sqrt{2}VAC_{MIN}$ .

Capacitor withstand voltage should be more than  $VIN_{MAX} = \sqrt{2} \times VAC_{MAX}$ ,  $VAC_{MAX}$  is the maximum AC input voltage.

It is also possible to follow the values of  $2\sim3uF/W$  for  $C_{BUS}$  at  $85VAC\sim265VAC$  and 1uF/W for  $C_{BUS}$  at  $195VAC\sim265VAC$ .

#### 13.3 Transformer Design

#### 13.3.1 Turns Ratio

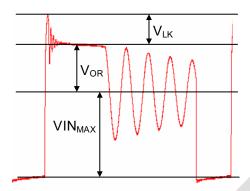

When the MOSFET is turned off, the drain leakage inductance spike voltage  $V_{LK}$ , the input voltage VIN, and the output voltage  $V_{OR}$  reflected to the primary will be applied to DS of the MOSFET.

The reflected voltage V<sub>OR</sub> is:

$$V_{OR} = V_{DS\_MAX} - V_{LK} - VIN_{MAX} - V_{MARGIN}$$

- V<sub>LK</sub> is the leakage inductance spike voltage

- V<sub>DS MAX</sub> is the maximum MOSFET voltage

- V<sub>MARGIN</sub> is the margin (100V for consumer, 300V for power)

From this, the turns ratio n can be calculated:

$$n = \frac{V_{OR}}{V_O + V_F}$$

V<sub>F</sub> is the output diode forward voltage drop

#### 13.3.2 Maximum Duty Cycle

$$D = \frac{V_{OR}}{V_{OR} + VIN_{MIN}}$$

VIN<sub>MIN</sub> is the DC voltage corresponding to the lowest AC input voltage

$$VIN_{MIN} = (0.7 \sim 0.9) \times \sqrt{2} \times VAC_{MIN}$$

Note: The maximum duty cycle D should not exceed the maximum duty cycle of the chip, and to leave some margin, it is recommended to be around 0.5.

#### 13.3.3 Peak Switching Current

The average input current I<sub>IN</sub> is calculated from the output power and the preset efficiency:

$$I_{IN} = \frac{P_O}{\eta \times VIN_{MIN}}$$

The primary inductor current ramp center value I<sub>L</sub> is:

$$I_L = \frac{I_{IN}}{D}$$

The peak switching current I<sub>PK</sub> is:

$$I_{PK} = (1 + \frac{r}{2}) \times I_L$$

$$r = \frac{\Delta I}{I}$$

Where "r" is the current ripple rate, it is recommended that "r" be taken as 1, and  $\Delta I$  is the variation of the primary inductor current.

#### 13.3.4 Primary-Side Inductance Value

$$L_P = \frac{VIN_{MIN} \times D}{I_L \times r \times F_{SW}}$$

Where  $F_{SW}$  is the switching frequency, and the typical value of the switching frequency of CN1102AC/D/E/F is 60KHz.

#### 13.3.5 Number of Winding Turns

Primary-side windings N<sub>P</sub>:

$$N_P = \frac{I_{PK} \times L_P}{B_{PK} \times A_e}$$

Where B<sub>PK</sub> is the maximum magnetic flux density at full load

$I_{PK} = I_L + 0.5 \times I_L \times r$  at full load,  $I_{PK} = 1.2 \times I_L + 0.5 \times I_L \times r$  at 120% load.

$$\frac{B_{PK}}{B_{MAX}} = \frac{1 + 0.5 \times r}{1.2 + 0.5 \times r}$$

The flux density  $B_{MAX}$  at 120% load is recommended not to exceed 0.35T, then the full load  $B_{PK}$  is not to exceed 0.31T when "r" is taken to be 1.

The effective cross-sectional area Ae of the core is obtained by selecting a suitable core according to the output power.

The number of turns N<sub>S</sub> of the secondary-side winding can be obtained as:

$$N_S = \frac{N_P}{n}$$

The VDD voltage range is 9V to 28V, taking the value of 15V at full load, and the number of turns of the auxiliary winding  $N_A$ :

$$N_A = N_S \times \frac{VDD + V_F}{V_O + V_F}$$

Where V<sub>F</sub> is the rectifier diode forward conduction drop voltage

#### 13.3.6 Calculation of Primary and Secondary Wire Diameters

The primary coil current RMS value I<sub>P RMS</sub> is:

$$I_{P\_RMS} = I_L \times \sqrt{\frac{D}{3} \times (3 + \frac{r^2}{4})}$$

The secondary coil current RMS value I<sub>S RMS</sub> is:

$$I_{S\_RMS} = n \times I_L \times \sqrt{\frac{1 - D}{3} \times (3 + \frac{r^2}{4})}$$

The cross-sectional area of the winding wire  $S = I_{RMS}/J$ , where "J" is the current density, generally taken as  $6\sim8A/mm^2$ .

The winding wire diameter d is

$$d = \sqrt{\frac{4 \times S}{\pi}}$$

#### 13.4 RCD Design

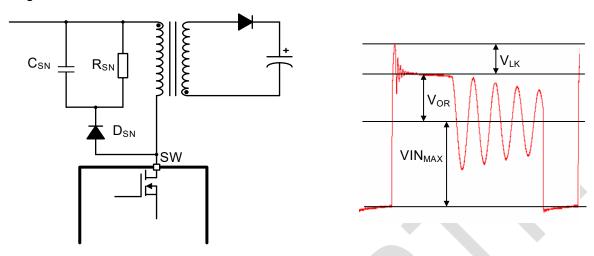

The following figure shows the reference diagram of the RCD absorption circuit with the  $V_{DS}$  waveform on the right.

In the right figure,  $V_{LK}$  is the leakage inductance spike voltage,  $V_{OR}$  is the transformer reflection voltage, the diode in the RCD circuit is recommended to choose a high voltage diode with a current capacity of 1A or more, and the capacitor is selected by the following formula:

$$P_{SN} = 0.5 \times L_{LK} \times I_{PK}^2 \times F_{SW} \times \frac{V_{LK} + V_{OR}}{V_{LK}}$$

$$R_{SN} = \frac{(V_{LK} + V_{OR}) \times V_{LK}}{0.5 \times L_{LK} \times I_{PK}^2 \times F_{SW}}$$

$$C_{SN} = \frac{V_{LK} + V_{OR}}{R_{SN} \times F_{SW} \times \Delta V_{SN}}$$

#### Among them:

- P<sub>SN</sub> is the leakage inductance loss

- L<sub>LK</sub> is the transformer leakage inductance

- I<sub>PK</sub> is the transformer peak current

- F<sub>SW</sub> is the switching frequency, typical value is 60KHz

- $\Delta V_{SN}$  is the capacitor ripple, according to experience, the value is generally taken as 10%~30% of the capacitor voltage.

#### 13.5 Selection of CS Resistance

The CS pin is the source of the internal integrated MOSFET. The CN1102AC/D/E/F has cycle-by-cycle overcurrent protection with  $V_{CS}$ =0.45V, and the peak current can be detected and controlled by the CS-to-ground resistor  $R_{CS}$ . Calculate the  $R_{CS}$  according to the following formula.

$$R_{CS} = \frac{V_{CS}}{I_{PK}}$$

#### 13.6 Selection of VDD Capacitor

VDD capacitor in the chip startup stage, the VDD capacitor is first charged through built-in high voltage starter MOS, and then discharge to maintain chip operation, so the choice of VDD capacitor directly affects the startup time, it is recommended 10uF ~ 47uF, the calculation formula is as follows:

$$T_{START} = \frac{C_{VDD} \times VDD}{I_{DD,CH}}$$

For example, if the VDD capacitance is selected to be 22uF,  $I_{DD\_CH}$  =1.5mA, and the startup voltage threshold of CN1102AC/D/E/F is 13V, the startup time is  $T_{START}$ =191mS.

#### 13.7 Selection of Output Rectifier Diode

The maximum reverse voltage V<sub>DR</sub> of the output rectifier diode and the current RMS value I<sub>D RMS</sub> are:

$$V_{DR} = V_O + \frac{VIN_{MAX}}{n}$$

$$I_{D\_RMS} = I_{S\_RMS} \times \sqrt{\frac{VIN_{MIN}}{V_{OR}}}$$

In practice, the maximum reverse voltage  $V_{RRM}$  and the average forward current  $I_F$  of the rectifier diode are margined as follows:

$$V_{RRM} > 1.3 \times V_{DR}$$

$I_F > 1.5 \times I_{D RMS}$

#### 13.8 Selection of Output Capacitor

The selection of the output capacitor mainly considers the RMS value of the ripple current, ESR and withstand voltage.

The ripple current I<sub>C RMS</sub> of the output capacitor is:

$$I_{C RMS} = \sqrt{(I_{D RMS})^2 - (I_0)^2}$$

The voltage ripple of the output capacitor is mainly caused by the charging and discharging of the capacitor and ESR.

The ripple caused by the charging and discharging of the capacitor is:

$$\Delta V_{CO} = \frac{I_O \times D}{C_O \times F_{SW}}$$

C<sub>O</sub> is the capacitance value

The ripple due to ESR is:

$$\Delta V_{ESR} = I_{PK} \times n \times R_{ESR}$$

R<sub>ESR</sub> is the ESR of the output capacitor

Since the electrolytic capacitor capacity is relatively large, the ripple due to ESR is mainly considered and  $R_{\text{ESR}}$  is calculated:

$$R_{ESR} = \frac{I_{PK} \times n}{\Delta V_{ESR}}$$

The withstand voltage of the output capacitor leaves a margin of at least 20% over the output voltage.

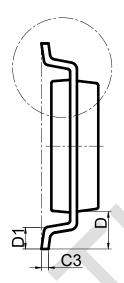

# 14 Package Information

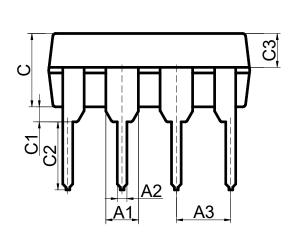

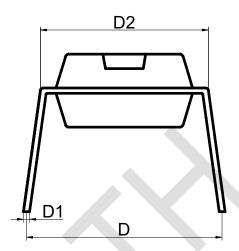

# DIP-7

| Dimension<br>Symbol | Min(mm) | Nom(mm) | Max(mm) |  |

|---------------------|---------|---------|---------|--|

| A                   | 9.15    | 9.25    | 9.35    |  |

| A1                  |         | 1.52REF |         |  |

| A2                  | 0.44    | -       | 0.52    |  |

| A3                  | 2.54BSC |         |         |  |

| В                   | 6.25    | 6.35    | 6.45    |  |

| С                   | 3.2     | 3.3     | 3.4     |  |

| C1                  | 0.51    | -       | -       |  |

| C2                  | 3       | -       | -       |  |

| C3                  | 1.55    | 1.6     | 1.65    |  |

| D                   | 7.62    | -       | 9.3     |  |

| D1                  | 0.25    | -       | 0.29    |  |

| D2                  | 7.62REF |         |         |  |

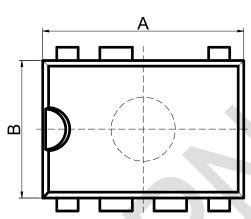

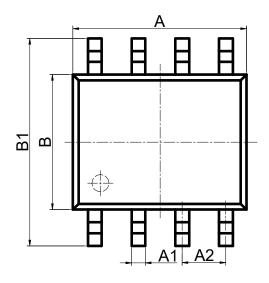

SOP-8

| Dimension Symbol | Min(mm) | Nom(mm) | Max(mm) |  |  |

|------------------|---------|---------|---------|--|--|

| A                | 4.80    | 4.90    | 5.00    |  |  |

| A1               | 0.39    | -       | 0.47    |  |  |

| A2               |         | 1.27BSC |         |  |  |

| В                | 3.80    | 3.90    | 4       |  |  |

| B1               | 5.80    | 6.00    | 6.20    |  |  |

| C                | 1.30    | 1.40    | 1.50    |  |  |

| C1               | 0.60    | 0.65    | 0.70    |  |  |

| C2               | 0.10    | -       | 0.225   |  |  |

| C3               | 0.20    | -       | 0.24    |  |  |

| D                | 1.05REF |         |         |  |  |

| D1               | 0.50    | -       | 0.80    |  |  |

| θ                | 0       | -       | 8°      |  |  |

#### **15 Important Statement**

Chipnorth Electronic Technology (Nanjing) Co., Ltd. and its subsidiaries reserve the right to make modifications, improvements, corrections, or other changes to this document and to any of the products described herein at any time without notice. Chipnorth Electronic Technology (Nanjing) Co., Ltd. disclaims any liability arising out of the use of this document or any of the products described herein; Chipnorth Electronic Technology (Nanjing) Co., Ltd. does not transfer any license to its patents or trademarks or other rights. Any customer or user using this document or any of the products described herein assumes all risk and agrees to hold harmless Chipnorth Electronic Technology (Nanjing) Co., Ltd. and all companies whose products are displayed on Chipnorth Electronic Technology (Nanjing) Co., Ltd. Chipnorth Electronic Technology (Nanjing) Co., Ltd. Chipnorth Electronic Technology (Nanjing) Co., Ltd. that a customer purchases or uses a product from Chipnorth Electronic Technology (Nanjing) Co., Ltd. for any unintended or unauthorized use, the customer shall indemnify and hold harmless Chipnorth Electronic Technology (Nanjing) Co., Ltd. and its representatives from and against all claims, damages, and attorney's fees arising from any personal injury or death, directly or indirectly, arising out of or in connection with such purchase or use.